FPGAپ@‰ٌکHƒuƒچƒbƒNپ@Tipsپ@پiڈ‰‹‰پj

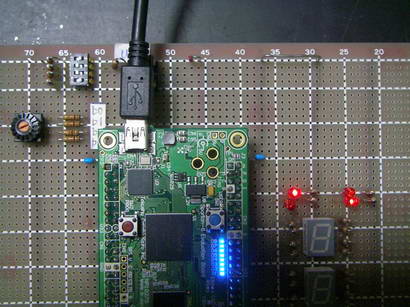

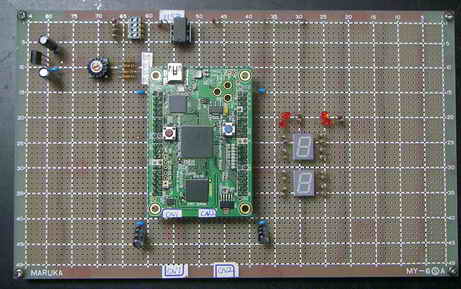

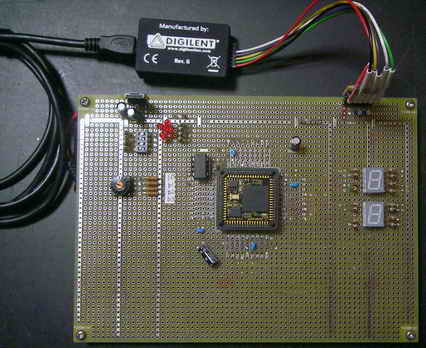

پ،پ@ƒXƒCƒbƒ`‚ة‚و‚éLED‚جONپEOFFپ@پ@پ@TKDN-SP6-45(Spartan-6)•ز

پ@پƒژژچى•iژd—lپ„

پ@پEƒIƒ‹ƒ^ƒlپ[ƒgƒXƒCƒbƒ`‚ة‚و‚èLED‚ًONپEOFF‚·‚邱‚ئ

پ@پE‰ٌکHگ”‚ح‚S‰ٌکH‚ئ‚·‚éپB

پ@پEFPGA‚حپ@ƒUƒCƒٹƒ“ƒNƒXپ@Spartan-6 XC6SLX45-CSG324 ‚ئ‚·‚éپB

پ@پEژg—p‚·‚é•]‰؟خق°ؤق‚حپ@“ءژê“dژq‰ٌکH‡ٹ TDKN-SP6-45‚ئ‚·‚éپB

پ@پƒژژچى•i‰ٌکHگ}پ„پ@پiپ¨پ@‰ٌکHگ}‚جPDFƒtƒ@ƒCƒ‹پj

پ@ژژچى•i‚ج‰ٌکHگ}‚ًژ¦‚µ‚ـ‚·پB

پƒژژچى•iٹOٹدپ„‰؛‹L‚جژتگ^‚ة‚حڈم‹L‰ٌکHگ}‚ة‚ح‚ب‚¢پA‚ـ‚½–{ƒeپ[ƒ}‚ئٹضŒW‚ج‚ب‚¢•”•i‚ھ‘½پXژت‚ء‚ؤ‚¢‚ـ‚·

پ@پƒƒvƒچƒOƒ‰ƒ€—لپ„

پƒvhdƒ\پ[ƒXƒtƒ@ƒCƒ‹پ„

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity f1112_SLX45_Led_OnOff2 is

Port ( Sw1 : in STD_LOGIC;

Sw2 : in STD_LOGIC;

Sw3 : in STD_LOGIC;

Sw4 : in STD_LOGIC;

Led1 : out STD_LOGIC;

Led2 : out STD_LOGIC;

Led3 : out STD_LOGIC;

Led4 : out STD_LOGIC);

end f1112_SLX45_Led_OnOff2;

architecture RTL of f1112_SLX45_Led_OnOff2 is

begin

Led1 <= not Sw1;

Led2 <= not Sw2;

Led3 <= not Sw3;

Led4 <= not Sw4;

end RTL;

--------------------------------------------------------------------------

پ@پ@پ@پ@پ@پ@پ@پ@پ@پƒucfƒ\پ[ƒXƒtƒ@ƒCƒ‹پ„ NET "Sw1" LOC = "N4"; NET "Sw2" LOC = "P4"; NET "Sw3" LOC = "N3"; NET "Sw4" LOC = "N5"; NET "Led1" LOC = "C6"; NET "Led2" LOC = "B2"; NET "Led3" LOC = "B3"; NET "Led4" LOC = "A2";

پƒ“®چىŒ‹‰تپ„

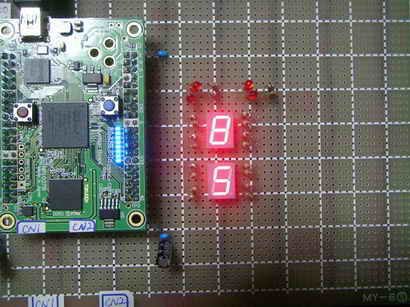

پ@ƒfƒBƒbƒvƒXƒCƒbƒ`‚إگشگFLED‚ھONپEOFF‚µ‚ؤ‚¢‚é‚ئ‚±‚ë‚جژتگ^‚إ‚·پB

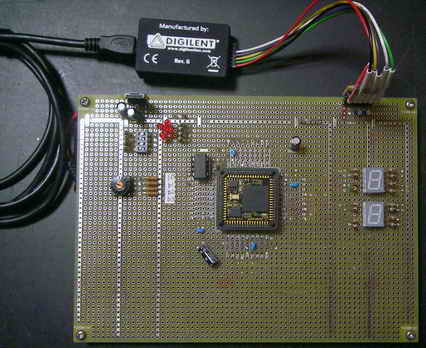

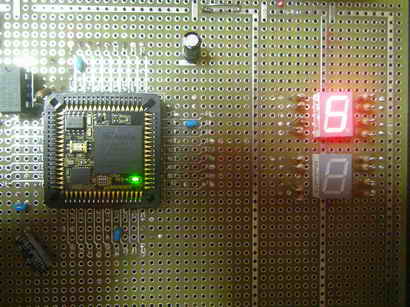

پ،پ@ƒXƒCƒbƒ`‚ة‚و‚éLED‚جONپEOFFپ@پ@پ@پ@پ@پ@پ@پ@XP68-01-LX16(Sprartan-6 PLCC)•ز

پƒژژچى•iژd—lپ„

پ@پEƒIƒ‹ƒ^ƒlپ[ƒgƒXƒCƒbƒ`‚ة‚و‚èLED‚ًONپEOFF‚·‚邱‚ئ

پ@پE‰ٌکHگ”‚ح‚S‰ٌکH‚ئ‚·‚éپB

پ@پEFPGA‚حپ@ƒUƒCƒٹƒ“ƒNƒXپ@Spartan-6 XC6SLX16-2CSG225C ‚ئ‚·‚éپB

پ@پEژg—p‚·‚é•]‰؟خق°ؤق‚حپ@(—L)ƒqƒ…پ[ƒ}ƒ“ƒfپ[ƒ^پ@ XP68-01-LX16پiٹOŒ`پFپ@PLCC 68ƒsƒ“‘ٹ“–پj ‚ئ‚·‚éپB

پ@پƒژژچى•i‰ٌکHگ}پ„پ@پiپ¨پ@‰ٌکHگ}‚جPDFƒtƒ@ƒCƒ‹پj

پ@ژژچى•i‚ج‰ٌکHگ}‚ًژ¦‚µ‚ـ‚·پB

پƒژژچى•iٹOٹدپ„‰؛‹L‚جژتگ^‚ة‚حڈم‹L‰ٌکHگ}‚ة‚ح‚ب‚¢پA‚ـ‚½–{ƒeپ[ƒ}‚ئٹضŒW‚ج‚ب‚¢•”•i‚ھ‘½پXژت‚ء‚ؤ‚¢‚ـ‚·

پƒƒvƒچƒOƒ‰ƒ€—لپ„ پƒvhdƒ\پ[ƒXƒtƒ@ƒCƒ‹پ„

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use Ieee.Std_Logic_Arith.All; use Ieee.Std_Logic_Unsigned.All; entity f1112_Xp68_16_Led_OnOff is Port ( Sw1 : in STD_LOGIC; Sw2 : in STD_LOGIC; Sw3 : in STD_LOGIC; Sw4 : in STD_LOGIC; Led1 : out STD_LOGIC; Led2 : out STD_LOGIC; Led3 : out STD_LOGIC; Led4 : out STD_LOGIC); end f1112_Xp68_16_Led_OnOff; architecture RTL of f1112_Xp68_16_Led_OnOff is begin Led1 <= not Sw1; Led2 <= not Sw2; Led3 <= not Sw3; Led4 <= not Sw4; end RTL;

پƒucfƒ\پ[ƒXƒtƒ@ƒCƒ‹پ„ # Xp68-16 Led On/Off NET "Sw1" LOC = "D4"; NET "Sw2" LOC = "E3"; NET "Sw3" LOC = "D3"; NET "Sw4" LOC = "D1"; NET "Led1" LOC = "B3"; NET "Led2" LOC = "A3"; NET "Led3" LOC = "C4"; NET "Led4" LOC = "A4";

پƒ“®چىŒ‹‰تپ„

پ@ƒfƒBƒbƒvƒXƒCƒbƒ`‚إگشگFLED‚ھONپEOFF‚µ‚ؤ‚¢‚é‚ئ‚±‚ë‚جژتگ^‚إ‚·پB

پ،پ@HEXƒXƒCƒbƒ`‚ة‚و‚é‚VƒZƒOƒپƒ“ƒgLED•\ژ¦پ@پ@پ@پ@پ@پ@TKDN-SP6-45(Spartan-6)پ@•زپ@پ@پ@پ@

پƒژژچى•iژd—lپ„

پ@پEپ@HEXپ@ƒXƒCƒbƒ`پi16گiƒXƒCƒbƒ`پj‚جگع“_ڈo—ح‚ًپ@‚VƒZƒOƒپƒ“ƒgLED‚ة•\ژ¦‚·‚éپB

پ@پE•\ژ¦•¶ژڑ”حˆح‚حپ@0 1 2 پcپ@C d E Fپ@‚ج16•¶ژڑ‚ئ‚·‚éپB

پ@پEFPGA‚حپ@ƒUƒCƒٹƒ“ƒNƒXپ@Spartan-6 XC6SLX45-CSG324 ‚ئ‚·‚éپB

پ@پEژg—p‚·‚é•]‰؟خق°ؤق‚حپ@“ءژê“dژq‰ٌکH‡ٹ TDKN-SP6-45‚ئ‚·‚éپB

پƒژژچى•i‰ٌکHگ}پ„پ@پiپ¨پ@‰ٌکHگ}‚جPDFƒtƒ@ƒCƒ‹پj

پ@ژژچى•i‚ج‰ٌکHگ}‚ًژ¦‚µ‚ـ‚·پB

پƒژژچى•iٹOٹدپ„‰؛‹L‚جژتگ^‚ة‚حڈم‹L‰ٌکHگ}‚ة‚ح‚ب‚¢پA‚ـ‚½–{ƒeپ[ƒ}‚ئٹضŒW‚ج‚ب‚¢•”•i‚ھ‘½پXژت‚ء‚ؤ‚¢‚ـ‚·

پƒƒvƒچƒOƒ‰ƒ€—لپ„

پƒvhdƒ\پ[ƒXƒtƒ@ƒCƒ‹پ„

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity f1112_SLX45_HexSw_7seg is

Port ( Hex_SW : in STD_LOGIC_VECTOR(3 downto 0);

Seg7_Led : out STD_LOGIC_VECTOR (7 downto 0));

end f1112_SLX45_HexSw_7seg;

architecture RTL of f1112_SLX45_HexSw_7seg is

signal nHex_Sw : std_logic_vector(3 downto 0);

begin

nHex_SW <= Hex_SW;

process(nHex_SW)

begin

case nHex_SW is --ٹesegmennt‚ئ‚جٹضŒW ".gfedcba"

when "0000" => seg7_Led(7 downto 0) <= "01000000"; --0

when "0001" => seg7_Led(7 downto 0) <= "01111001"; --1

when "0010" => seg7_Led(7 downto 0) <= "00100100"; --2

when "0011" => seg7_Led(7 downto 0) <= "00110000"; --3

when "0100" => seg7_Led(7 downto 0) <= "00011001"; --4

when "0101" => seg7_Led(7 downto 0) <= "00010010"; --5

when "0110" => seg7_Led(7 downto 0) <= "00000010"; --6

when "0111" => seg7_Led(7 downto 0) <= "01111000"; --7

when "1000" => seg7_Led(7 downto 0) <= "00000000"; --8

when "1001" => seg7_Led(7 downto 0) <= "00010000"; --9

when "1010" => seg7_Led(7 downto 0) <= "00001000"; --A

when "1011" => seg7_Led(7 downto 0) <= "00000011"; --b

when "1100" => seg7_Led(7 downto 0) <= "01000110"; --C

when "1101" => seg7_Led(7 downto 0) <= "00100001"; --d

when "1110" => seg7_Led(7 downto 0) <= "00000110"; --E

when "1111" => seg7_Led(7 downto 0) <= "00001110"; --F

when others => seg7_Led(7 downto 0) <= "00000000"; --‚»‚ج‘¼‚جڈêچ‡

end case;

end process;

end RTL;

پƒucfƒ\پ[ƒXƒtƒ@ƒCƒ‹پ„

# in Port NET "Hex_SW<0>" LOC = "V4"; NET "Hex_SW<1>" LOC = "T3"; NET "Hex_SW<2>" LOC = "T4"; NET "Hex_SW<3>" LOC = "R3"; # out Port NET "Seg7_Led<0>" LOC = "A10"; NET "Seg7_Led<1>" LOC = "C10"; NET "Seg7_Led<2>" LOC = "C8"; NET "Seg7_Led<3>" LOC = "D8"; NET "Seg7_Led<4>" LOC = "A6"; NET "Seg7_Led<5>" LOC = "C7"; NET "Seg7_Led<6>" LOC = "A5"; NET "Seg7_Led<7>" LOC = "B6";

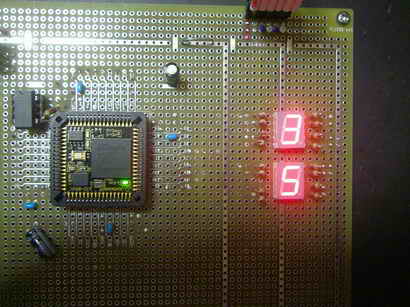

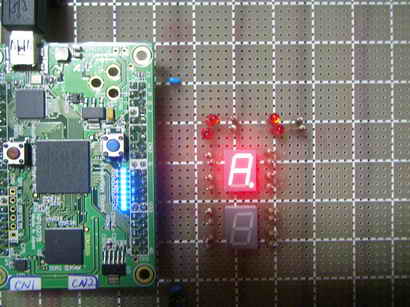

پƒ“®چىŒ‹‰تپ„

پ@پEHEXپ@ƒXƒCƒbƒ`‚جگMچ†‚ھپ@10پi10گiگ”پj‚جڈêچ‡‚جژتگ^‚إپAپ@‚VƒZƒOƒپƒ“ƒgLED‚ة‚حA‚ھ•\ژ¦‚³‚ê‚ؤ‚¢‚ـ‚·پB

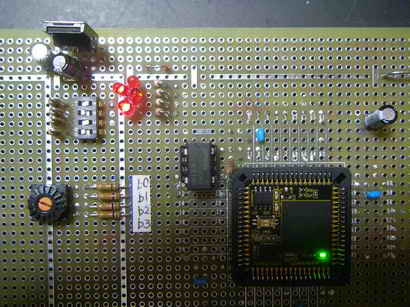

پ،پ@پ@HEXƒXƒCƒbƒ`‚ة‚و‚é‚VƒZƒOƒپƒ“ƒgLED•\ژ¦پ@پ@پ@پ@پ@پ@پ@XP68-01-LX16(Sprartan-6 PLCC)•ز

پƒژژچى•iژd—lپ„

پ@پEپ@HEXپ@ƒXƒCƒbƒ`پi16گiƒXƒCƒbƒ`پj‚جگع“_ڈo—ح‚ًپ@‚VƒZƒOƒپƒ“ƒgLED‚ة•\ژ¦‚·‚éپB

پ@پE•\ژ¦•¶ژڑ”حˆح‚حپ@0 1 2 پcپ@C d E Fپ@‚ج16•¶ژڑ‚ئ‚·‚éپB

پ@پEFPGA‚حپ@ƒUƒCƒٹƒ“ƒNƒXپ@Spartan-6 XC6SLX16-2CSG225C ‚ئ‚·‚éپB

پ@پEژg—p‚·‚é•]‰؟خق°ؤق‚حپ@(—L)ƒqƒ…پ[ƒ}ƒ“ƒfپ[ƒ^پ@ XP68-01-LX16پiٹOŒ`پFپ@PLCC 68ƒsƒ“‘ٹ“–پj ‚ئ‚·‚éپB

پƒژژچى•i‰ٌکHگ}پ„پ@پiپ¨پ@‰ٌکHگ}‚جPDFƒtƒ@ƒCƒ‹پj

پ@ژژچى•i‚ج‰ٌکHگ}‚ًژ¦‚µ‚ـ‚·پB

پƒژژچى•iٹOٹدپ„‰؛‹L‚جژتگ^‚ة‚حڈم‹L‰ٌکHگ}‚ة‚ح‚ب‚¢پA‚ـ‚½–{ƒeپ[ƒ}‚ئٹضŒW‚ج‚ب‚¢•”•i‚ھ‘½پXژت‚ء‚ؤ‚¢‚ـ‚·

پƒƒvƒچƒOƒ‰ƒ€—لپ„

پƒvhdƒ\پ[ƒXƒtƒ@ƒCƒ‹پ„

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_logic_Arith.All;

use Ieee.Std_logic_Unsigned.All;

entity f1112_Xp68_16_HexSw_7seg is

Port ( Hex_SW : in Std_Logic_Vector(3 downto 0);

Seg7_Led : out STD_LOGIC_VECTOR (7 downto 0));

end f1112_Xp68_16_HexSw_7seg;

architecture RTL of f1112_Xp68_16_HexSw_7seg is

signal nHex_Sw : Std_Logic_Vector(3 downto 0);

begin

nHex_Sw <= not Hex_Sw;

process(nHex_Sw)

begin

case nHex_SW is --ٹesegmennt‚ئ‚جٹضŒW ".gfedcba"

when "0000" => seg7_Led(7 downto 0) <= "01000000"; --0

when "0001" => seg7_Led(7 downto 0) <= "01111001"; --1

when "0010" => seg7_Led(7 downto 0) <= "00100100"; --2

when "0011" => seg7_Led(7 downto 0) <= "00110000"; --3

when "0100" => seg7_Led(7 downto 0) <= "00011001"; --4

when "0101" => seg7_Led(7 downto 0) <= "00010010"; --5

when "0110" => seg7_Led(7 downto 0) <= "00000010"; --6

when "0111" => seg7_Led(7 downto 0) <= "01111000"; --7

when "1000" => seg7_Led(7 downto 0) <= "00000000"; --8

when "1001" => seg7_Led(7 downto 0) <= "00010000"; --9

when "1010" => seg7_Led(7 downto 0) <= "00001000"; --A

when "1011" => seg7_Led(7 downto 0) <= "00000011"; --b

when "1100" => seg7_Led(7 downto 0) <= "01000110"; --C

when "1101" => seg7_Led(7 downto 0) <= "00100001"; --d

when "1110" => seg7_Led(7 downto 0) <= "00000110"; --E

when "1111" => seg7_Led(7 downto 0) <= "00001110"; --F

when others => seg7_Led(7 downto 0) <= "00000000"; --‚»‚ج‘¼‚جڈêچ‡

end case;

end process;

end RTL;

پƒucfƒ\پ[ƒXƒtƒ@ƒCƒ‹پ„ # f1112_Xp68_16_HexSw_7seg NET "Hex_Sw<0>" LOC = "C2"; NET "Hex_Sw<1>" LOC = "C1"; NET "Hex_Sw<2>" LOC = "E2"; NET "Hex_Sw<3>" LOC = "E1"; NET "Seg7_Led<0>" LOC = "A7"; NET "Seg7_Led<1>" LOC = "B7"; NET "Seg7_Led<2>" LOC = "A13"; NET "Seg7_Led<3>" LOC = "B13"; NET "Seg7_Led<4>" LOC = "A11"; NET "Seg7_Led<5>" LOC = "B11"; NET "Seg7_Led<6>" LOC = "A6"; NET "Seg7_Led<7>" LOC = "F3";

--------------------------------------------

پƒ“®چىŒ‹‰تپ„

پ@‚W‚ج‚و‚¤‚ةŒ©‚¦‚ـ‚·‚ھپ@‚T‚ً•\ژ¦‚µ‚½ژ‚جژتگ^‚إ‚·پB

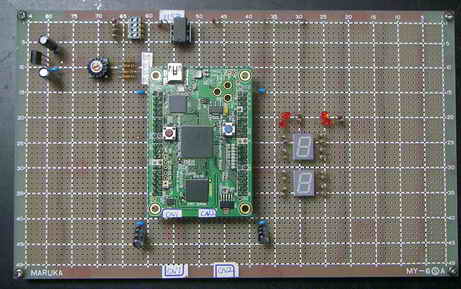

پ،پ@پ@ƒtƒٹپ[ƒ‰ƒ“ƒJƒEƒ“ƒ^پi‚VƒZƒOƒپƒ“ƒgLEDپ@‚P‚Oگi‚QŒ…پjپ@پ@پ@پ@TKDN-SP6-45(Spartan-6)•ز

پƒژژچى•iژd—lپ„

پ@پEFPGA‚جٹO•”‚ة1MH‚ڑ‚ج”گUٹي‚ًگع‘±‚µ‚ؤ‚±‚جƒpƒ‹ƒX‚ً‚à‚ئ‚ة‚P•b‚²‚ئ‚ةƒCƒ“ƒNƒٹƒپƒ“ƒg‚·‚éƒJƒEƒ“ƒ^‚ً‚آ‚‚éپB

پ@پE•\ژ¦‚ح0پ`99‚ـ‚إ‚ج10گiگ®گ”‚ئ‚·‚éپBپ@99‚ج‚ ‚ئ‚ح0‚ة–ك‚邱‚ئ

پ@پE•\ژ¦‚ح‚Q‚آ‚ج‚VƒZƒOƒپƒ“ƒgLED‚ًژg—p‚·‚邱‚ئ

پ@پEFPGA‚حپ@ƒUƒCƒٹƒ“ƒNƒXپ@Spartan-6 XC6SLX45-CSG324 ‚ئ‚·‚éپB

پ@پEژg—p‚·‚é•]‰؟خق°ؤق‚حپ@“ءژê“dژq‰ٌکH‡ٹ TDKN-SP6-45‚ئ‚·‚éپB

پ@

پƒژژچى•i‰ٌکHگ}پ„پ@پiپ¨پ@‰ٌکHگ}‚جPDFƒtƒ@ƒCƒ‹پj

پ@ژژچى•i‚ج‰ٌکHگ}‚ًژ¦‚µ‚ـ‚·پB

پƒژژچى•iٹOٹدپ„‰؛‹L‚جژتگ^‚ة‚حڈم‹L‰ٌکHگ}‚ة‚ح‚ب‚¢پA‚ـ‚½–{ƒeپ[ƒ}‚ئٹضŒW‚ج‚ب‚¢•”•i‚ھ‘½پXژت‚ء‚ؤ‚¢‚ـ‚·

پƒƒvƒچƒOƒ‰ƒ€—لپ„

پƒvhdƒ\پ[ƒXƒtƒ@ƒCƒ‹پ„

library IEEE; --چإڈم‘wƒuƒچƒbƒN

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity f1112_SLX45_FreeCounter_10MHz is

Port ( Clk : in STD_LOGIC;

Seg7_0 : out STD_LOGIC_VECTOR (7 downto 0);

Seg7_1 : out STD_LOGIC_VECTOR (7 downto 0));

end f1112_SLX45_FreeCounter_10MHz;

architecture RTL of f1112_SLX45_FreeCounter_10MHz is

Signal Count1: Integer range 0 to 10000000;

Signal Count2: Integer range 0 to 9;

Signal Count3: Integer range 0 to 9;

component Display0 is --ƒRƒ“ƒ|پ[ƒlƒ“ƒgگ錾

Port ( Count2 : in Integer range 0 to 10;

Seg7_0 : out STD_LOGIC_VECTOR (7 downto 0));

end component;

component Display1 is --ƒRƒ“ƒ|پ[ƒlƒ“ƒgگ錾

Port ( Count3 : in Integer range 0 to 10;

Seg7_1 : out STD_LOGIC_VECTOR (7 downto 0));

end component;

begin

process(Clk)

begin

if(Clk' event and Clk = '1')then --1msec–ˆ

Count1 <= Count1 + 1;

if(Count1 >= 10000000)then --1sec–ˆ

Count1 <= 0;

Count2 <= Count2 +1; --0پ`1‚T‚جŒJ‚è•ش‚µ

if(Count2 >= 9)then

Count2 <= 0;

Count3 <= Count3 + 1;

if(Count3 >= 9)then

Count3 <= 0;

end if;

end if;

end if;

end if;

end process;

U1: Display0 port map(Count2,Seg7_0);

U2: Display1 port map(Count3,Seg7_1);

end RTL;

----------------------------------------------------------------------

library IEEE; --‰؛ˆت‘wƒuƒچƒbƒN

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_Arith.All;

use Ieee.Std_Logic_Unsigned.All;

entity Display1 is --‚VƒZƒOƒپƒ“ƒgLED•\ژ¦ƒ‰ƒCƒuƒ‰ƒٹ

Port ( Count3 : in Integer range 0 to 10;

Seg7_1 : out STD_LOGIC_VECTOR (7 downto 0));

end Display1;

architecture RTL of Display1 is

begin

process(Count3) --‚VƒZƒOƒپƒ“ƒgLEDپ@16گi•\ژ¦

begin

case(Count3) is

when 0 => Seg7_1 <= "11000000"; --0

when 1 => Seg7_1 <= "11111001"; --1

when 2 => Seg7_1 <= "10100100"; --2

when 3 => Seg7_1 <= "10110000"; --3

when 4 => Seg7_1 <= "10011001"; --4

when 5 => Seg7_1 <= "10010010"; --5

when 6 => Seg7_1 <= "10000010"; --6

when 7 => Seg7_1<= "11111000"; --7

when 8 => Seg7_1 <= "10000000"; --8

when 9 => Seg7_1 <= "10010000"; --9

when 10 => Seg7_1 <= "10001000"; --A

when others => Seg7_1 <="10000110"; --‚»‚ج‘¼‚جڈêچ‡

end case;

end process;

end RTL;

--------------------------------------------------------------------------

library IEEE; --‰؛ˆت‘wƒuƒچƒbƒN

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_Arith.All;

use Ieee.Std_Logic_Unsigned.All;

entity Display0 is --‚VƒZƒOƒپƒ“ƒgLED•\ژ¦ƒ‰ƒCƒuƒ‰ƒٹ

Port ( Count2 : in Integer range 0 to 10;

Seg7_0 : out STD_LOGIC_VECTOR (7 downto 0));

end Display0;

architecture RTL of Display0 is

begin

process(Count2) --‚VƒZƒOƒپƒ“ƒgLEDپ@16گi•\ژ¦

begin

case(Count2) is

when 0 => Seg7_0 <= "11000000"; --0

when 1 => Seg7_0 <= "11111001"; --1

when 2 => Seg7_0 <= "10100100"; --2

when 3 => Seg7_0 <= "10110000"; --3

when 4 => Seg7_0 <= "10011001"; --4

when 5 => Seg7_0 <= "10010010"; --5

when 6 => Seg7_0 <= "10000010"; --6

when 7 => Seg7_0 <= "11111000"; --7

when 8 => Seg7_0 <= "10000000"; --8

when 9 => Seg7_0 <= "10010000"; --9

when 10 => Seg7_0 <= "10001000"; --A

when others => Seg7_0 <="10000110"; --‚»‚ج‘¼‚جڈêچ‡

end case;

end process;

end RTL;

پƒucfƒ\پ[ƒXƒtƒ@ƒCƒ‹پ„ # C1112_SLX45_FeerunCounter_10MHz.ucf NET "Clk" LOC = "T8"; NET "Seg7_0<0>" LOC = "A10" ; NET "Seg7_0<1>" LOC = "C10" ; NET "Seg7_0<2>" LOC = "C8" ; NET "Seg7_0<3>" LOC = "D8" ; NET "Seg7_0<4>" LOC = "A6" ; NET "Seg7_0<5>" LOC = "C7" ; NET "Seg7_0<6>" LOC = "A5" ; NET "Seg7_0<7>" LOC = "B6" ; NET "seg7_1<0>" LOC = "B14" ; NET "seg7_1<1>" LOC = "A14" ; NET "seg7_1<2>" LOC = "C13" ; NET "seg7_1<3>" LOC = "A13" ; NET "seg7_1<4>" LOC = "B12" ; NET "seg7_1<5>" LOC = "A12" ; NET "seg7_1<6>" LOC = "B11" ; NET "seg7_1<7>" LOC = "A11" ; }

-------------------------------------------

پƒ“®چىŒ‹‰تپ„

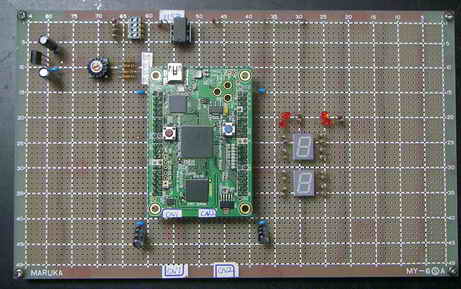

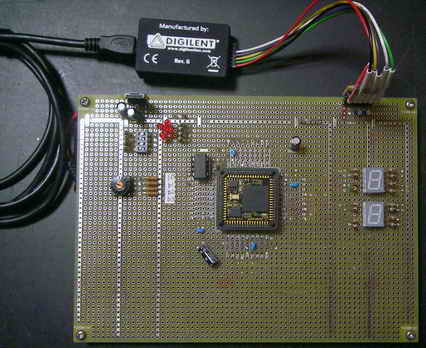

پ@ƒJƒEƒ“ƒgگ”58‚جژ‚جژتگ^‚إ‚·پBپ@ڈم’i‚ھ‚PŒ…–ع‚جگ”ژڑ‚ًپA‰؛’i‚ھ‚QŒ…–ع‚جگ”ژڑ‚ً•\‚µ‚ـ‚·پB

پ،پ@پ@ƒtƒٹپ[ƒ‰ƒ“ƒJƒEƒ“ƒ^پi‚VƒZƒOƒپƒ“ƒgLEDپ@‚P‚Oگi‚QŒ…پjپ@پ@پ@پ@پ@پ@XP68-01-LX16(Sprartan-6 PLCC)•ز

پƒژژچى•iژd—lپ„

پ@پEFPGA‚جٹO•”‚ة1MH‚ڑ‚ج”گUٹي‚ًگع‘±‚µ‚ؤ‚±‚جƒpƒ‹ƒX‚ً‚à‚ئ‚ة‚P•b‚²‚ئ‚ةƒCƒ“ƒNƒٹƒپƒ“ƒg‚·‚éƒJƒEƒ“ƒ^‚ً‚آ‚‚éپB

پ@پE•\ژ¦‚ح0پ`99‚ـ‚إ‚ج10گiگ®گ”‚ئ‚·‚éپBپ@99‚ج‚ ‚ئ‚ح0‚ة–ك‚邱‚ئ

پ@پE•\ژ¦‚ح‚Q‚آ‚ج‚VƒZƒOƒپƒ“ƒgLED‚ًژg—p‚·‚邱‚ئ

پ@پEFPGA‚حپ@ƒUƒCƒٹƒ“ƒNƒXپ@Spartan-6 XC6SLX16-2CSG225C ‚ئ‚·‚éپB

پ@پEژg—p‚·‚é•]‰؟خق°ؤق‚حپ@(—L)ƒqƒ…پ[ƒ}ƒ“ƒfپ[ƒ^پ@ XP68-01-LX16پiٹOŒ`پFپ@PLCC 68ƒsƒ“‘ٹ“–پj ‚ئ‚·‚éپB

پ@

پƒژژچى•i‰ٌکHگ}پ„پ@پiپ¨پ@‰ٌکHگ}‚جPDFƒtƒ@ƒCƒ‹پj

پ@ژژچى•i‚ج‰ٌکHگ}‚ًژ¦‚µ‚ـ‚·پB

پƒژژچى•iٹOٹدپ„‰؛‹L‚جژتگ^‚ة‚حڈم‹L‰ٌکHگ}‚ة‚ح‚ب‚¢پA‚ـ‚½–{ƒeپ[ƒ}‚ئٹضŒW‚ج‚ب‚¢•”•i‚ھ‘½پXژت‚ء‚ؤ‚¢‚ـ‚·

پƒƒvƒچƒOƒ‰ƒ€—لپ„

پƒvhdƒ\پ[ƒXƒtƒ@ƒCƒ‹پ„

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_1164.All;

use Ieee.Std_Logic_1164.All;

entity f1112_Xp68_16_FreeRun_Counter_10MH is

Port ( Clk : in STD_LOGIC;

Seg7_0 : out STD_LOGIC_VECTOR (7 downto 0);

Seg7_1 : out STD_LOGIC_VECTOR (7 downto 0));

end f1112_Xp68_16_FreeRun_Counter_10MH;

architecture RTL of f1112_Xp68_16_FreeRun_Counter_10MH is

Signal Count1: Integer range 0 to 10000000;

Signal Count2: Integer range 0 to 9;

Signal Count3: Integer range 0 to 9;

component Display0 is --ƒRƒ“ƒ|پ[ƒlƒ“ƒgگ錾

Port ( Count2 : in Integer range 0 to 10;

Seg7_0 : out STD_LOGIC_VECTOR (7 downto 0));

end component;

component Display1 is --ƒRƒ“ƒ|پ[ƒlƒ“ƒgگ錾

Port ( Count3 : in Integer range 0 to 10;

Seg7_1 : out STD_LOGIC_VECTOR (7 downto 0));

end component;

begin

process(Clk)

begin

if(Clk' event and Clk = '1')then --1msec–ˆ

Count1 <= Count1 + 1;

if(Count1 >= 10000000)then --1sec–ˆ

Count1 <= 0;

Count2 <= Count2 +1; --0پ`1‚T‚جŒJ‚è•ش‚µ

if(Count2 >= 9)then

Count2 <= 0;

Count3 <= Count3 + 1;

if(Count3 >= 9)then

Count3 <= 0;

end if;

end if;

end if;

end if;

end process;

U1: Display0 port map(Count2,Seg7_0);

U2: Display1 port map(Count3,Seg7_1);

end RTL;

----------------------------------------------------------------------

library IEEE; --‰؛ˆت‘wƒuƒچƒbƒN

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_Arith.All;

use Ieee.Std_Logic_Unsigned.All;

entity Display1 is --‚VƒZƒOƒپƒ“ƒgLED•\ژ¦ƒ‰ƒCƒuƒ‰ƒٹ

Port ( Count3 : in Integer range 0 to 10;

Seg7_1 : out STD_LOGIC_VECTOR (7 downto 0));

end Display1;

architecture RTL of Display1 is

begin

process(Count3) --‚VƒZƒOƒپƒ“ƒgLEDپ@16گi•\ژ¦

begin

case(Count3) is

when 0 => Seg7_1 <= "11000000"; --0

when 1 => Seg7_1 <= "11111001"; --1

when 2 => Seg7_1 <= "10100100"; --2

when 3 => Seg7_1 <= "10110000"; --3

when 4 => Seg7_1 <= "10011001"; --4

when 5 => Seg7_1 <= "10010010"; --5

when 6 => Seg7_1 <= "10000010"; --6

when 7 => Seg7_1<= "11111000"; --7

when 8 => Seg7_1 <= "10000000"; --8

when 9 => Seg7_1 <= "10010000"; --9

when 10 => Seg7_1 <= "10001000"; --A

end case;

end process;

end RTL;

--------------------------------------------------------------------------

library IEEE; --‰؛ˆت‘wƒuƒچƒbƒN

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_Arith.All;

use Ieee.Std_Logic_Unsigned.All;

entity Display0 is --‚VƒZƒOƒپƒ“ƒgLED•\ژ¦ƒ‰ƒCƒuƒ‰ƒٹ

Port ( Count2 : in Integer range 0 to 10;

Seg7_0 : out STD_LOGIC_VECTOR (7 downto 0));

end Display0;

architecture RTL of Display0 is

begin

process(Count2) --‚VƒZƒOƒپƒ“ƒgLEDپ@16گi•\ژ¦

begin

case(Count2) is

when 0 => Seg7_0 <= "11000000"; --0

when 1 => Seg7_0 <= "11111001"; --1

when 2 => Seg7_0 <= "10100100"; --2

when 3 => Seg7_0 <= "10110000"; --3

when 4 => Seg7_0 <= "10011001"; --4

when 5 => Seg7_0 <= "10010010"; --5

when 6 => Seg7_0 <= "10000010"; --6

when 7 => Seg7_0 <= "11111000"; --7

when 8 => Seg7_0 <= "10000000"; --8

when 9 => Seg7_0 <= "10010000"; --9

when 10 => Seg7_0 <= "10001000"; --A

end case;

end process;

end RTL;

پƒurfƒ\پ[ƒXƒtƒ@ƒCƒ‹پ„ #f1112_Xp68_16_FreeRun_Counter_10MHz NET "Clk" LOC = "J2"; NET "Seg7_0<0>" LOC = "A7"; NET "Seg7_0<1>" LOC = "B7"; NET "Seg7_0<2>" LOC = "A13"; NET "Seg7_0<3>" LOC = "B13"; NET "Seg7_0<4>" LOC = "A11"; NET "Seg7_0<5>" LOC = "B11"; NET "Seg7_0<6>" LOC = "A6"; NET "Seg7_0<7>" LOC = "F3"; NET "Seg7_1<0>" LOC = "M4"; NET "Seg7_1<1>" LOC = "C8"; NET "Seg7_1<2>" LOC = "A9"; NET "Seg7_1<3>" LOC = "B9"; NET "Seg7_1<4>" LOC = "C11"; NET "Seg7_1<5>" LOC = "D11"; NET "Seg7_1<6>" LOC = "A12"; NET "Seg7_1<7>" LOC = "C12";

----------------------------------------------

پƒ“®چىŒ‹‰تپ„

پ@ƒJƒEƒ“ƒgگ”‚ھ53‚جژ‚جژتگ^‚إ‚·پBپ@ڈم’i‚ھ1Œ…–عپA‰؛’i‚ھ2Œ…–ع‚جگ”ژڑ‚ً•\ژ¦‚µ‚ؤ‚¢‚ـ‚·پB