丂VHDL丂婎慴丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂![]() 丂丂

丂丂![]()

仭丂墘嶼巕

丂丂仭榑棟墘嶼巕丂丂丂not丂乮斲掕乯

丂丂丂丂丂CPLD傪偼偠傔偰摦嶌偝傞偲偒偺僔儞僾儖偱 庤偛傠側僒儞僾儖傪徯夘偟傑偡丅

丂丂丂

丂丂丂丂亙帋嶌昳巇條亜

丂丂丂丂丂丒讲怣崋傪CPLD偵擖椡偡傞丅

丂丂丂丂丂丒CPLD撪偱偼丂擖椡偟偰偒偨僗僀僢僠怣崋傪墘嶼巕not傪偮偐偭偨夞楬偱斀揮偝偣傞丅

丂丂丂丂丂丒擖椡怣崋偑侾乮乭High乭丄SW丗off乯偺応崌LED傪揰摂偝偣丄侽乮乭Low乭丄SW丗on乯偺応崌偼LED傪徚摂偝偣傞丅

丂丂丂丂

丂丂亙帋嶌昳夞楬恾亜(仺夞楬恾偺PDF僼傽僀儖乯

丂丂丂丂僓僀儕儞僋僗丂XC9572XL傪偮偐偭偨応崌偺夞楬恾傪埲壓偵帵偟傑偡丅

丂

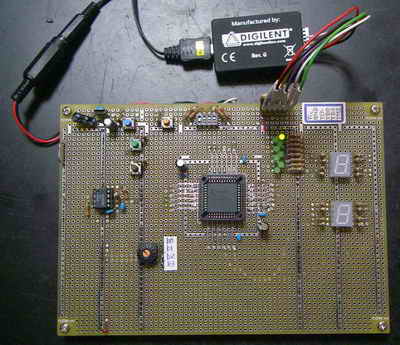

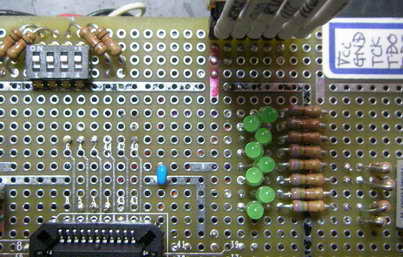

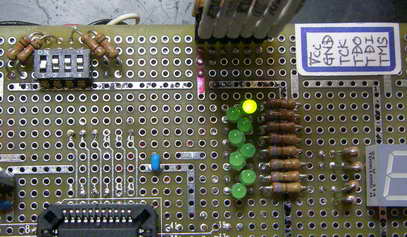

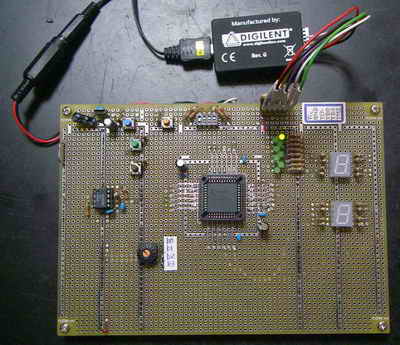

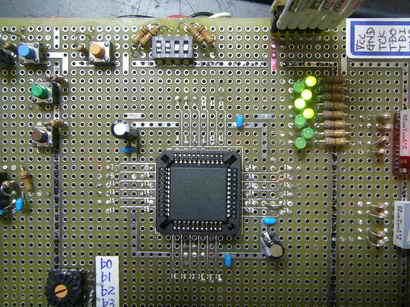

亙帋嶌昳奜娤亜壓婰偺幨恀偵偼忋婰夞楬恾偵偼側偄丄傑偨杮僥乕儅偲娭學偺側偄晹昳偑懡乆幨偭偰偄傑偡

丂丂丂丂丂丂丂丂丂丂

婰弎椺 亙VHDL僜乕僗僼傽僀儖亜

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity c1110_Not is Port ( Sw1 : in STD_LOGIC; Led1 : out STD_LOGIC); end c1110_Not; architecture RTL of c1110_Not is begin Led1 <= not Sw1; --丂斲掕丗丂not end RTL; ---------------------------------------------------------------------- --------------------------------------------------------------------- --亙ucf僜乕僗僼傽僀儖亜 #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "Led1" LOC = "P44" ; NET "Sw1" LOC = "P1" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

亙摦嶌寢壥亜

| 丂 丂儌乕僪 |

EUT幨恀 |

| 丂丂SW侾丗丂ON丂 丂丂LED1丗丂OFF丂 |

|

| 丂丂SW1丗丂OFF丂 丂丂LED侾丗丂ON丂 |

|

丂丂仭丂榑棟墘嶼巕丂丂丂and乮榑棟愊乯丄or乮榑棟榓乯丄nand乮斲掕榑棟愊乯丄nor乮斲掕榑棟榓乯丄xor乮攔懠揑榑棟榓乯

丂亙帋嶌昳巇條亜

丂丂嘆丂SW侾偲SW俀偑嫟偵侾乮off乯側傜LED侾偼徚摂偟丄偦偺懠偺応崌偼揰摂偡傞偙偲丅乮and乯

丂丂嘇丂SW俁傑偨偼SW係偺偄偢傟偐偑侾乮off乯側傜LED俀偼徚摂偡傞偙偲丅偦偺懠偺応崌偼揰摂偡傞偙偲丅乮or乯

丂丂嘊丂SW俆偲SW俇偑嫟偵侾乮off乯側傜LED俁偼揰摂偟丄偦偺懠偺応崌偼徚摂偡傞偙偲乮nand乯

丂丂嘋丂SW俈傑偨偼SW俉偺偄偢傟偐偑侾乮off乯側傜LED係偼揰摂偡傞偙偲丅偦偺懠偺応崌偼徚摂偺偙偲乮nor乯

丂丂嘍丂HEX僗僠僢僠偺SW侾偲SW俀偑嫟偵侾乮off乯偱偁傞偐丄傑偨偼嫟偵侽乮on乯偱偁傞応崌偼LED俆徚摂偟丄偦偺懠偺応崌偼揰摂偡傞偙偲乮xor乯

丂丂亙帋嶌昳夞楬恾亜(仺夞楬恾偺PDF僼傽僀儖乯

丂丂丂丂僓僀儕儞僋僗丂XC9572XL傪偮偐偭偨応崌偺夞楬恾傪埲壓偵帵偟傑偡丅

丂亙帋嶌昳奜娤亜壓婰偺幨恀偵偼忋婰夞楬恾偵偼側偄丄傑偨杮僥乕儅偲娭學偺側偄晹昳偑懡乆幨偭偰偄傑偡

亙僾儘僌儔儉亜

亙VHDL僜乕僗僼傽僀儖亜

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity c1110_and_or_nand_nor_xor is

Port ( Sw1 : in STD_LOGIC;

Sw2 : in STD_LOGIC;

Sw3 : in STD_LOGIC;

Sw4 : in STD_LOGIC;

Sw5 : in STD_LOGIC;

Sw6 : in STD_LOGIC;

Sw7 : in STD_LOGIC;

Sw8 : in STD_LOGIC;

Hex_Sw1 : in STD_LOGIC;

Hex_Sw2 : in STD_LOGIC;

Led1 : out STD_LOGIC;

Led2 : out STD_LOGIC;

Led3 : out STD_LOGIC;

Led4 : out STD_LOGIC;

Led5 : out STD_LOGIC);

end c1110_and_or_nand_nor_xor;

architecture RTL of c1110_and_or_nand_nor_xor is

begin

Led1 <= Sw1 and Sw2; --榑棟愊

Led2 <= Sw3 or Sw4; --榑棟榓

Led3 <= Sw5 nand Sw6; --斲掕揑榑棟愊

Led4 <= Sw7 nor Sw8; --斲掕揑榑棟榓

Led5 <= Hex_Sw1 xor Hex_Sw2; --攔懠揑榑棟榓

end RTL;

---------------------------------------------------------------------------------------------- -------------------------------------------------------------------------------------------- --亙ucf僜乕僗僼傽僀儖亜 #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "Hex_Sw1" LOC = "P14" ; NET "Hex_Sw2" LOC = "P13" ; NET "Led1" LOC = "P44" ; NET "Led2" LOC = "P43" ; NET "Led3" LOC = "P40" ; NET "Led4" LOC = "P39" ; NET "Led5" LOC = "P38" ; NET "Sw1" LOC = "P1" ; NET "Sw2" LOC = "P2" ; NET "Sw3" LOC = "P3" ; NET "Sw4" LOC = "P4" ; NET "Sw5" LOC = "P6" ; NET "Sw6" LOC = "P7" ; NET "Sw7" LOC = "P8" ; NET "Sw8" LOC = "P9" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

亙摦嶌寢壥亜

仭丂娭學墘嶼巕丄壛朄墘嶼巕丄忔朄墘嶼巕丄僔僼僩墘嶼巕丄偦偺懠墘嶼巕

丂丂榑棟墘嶼巕偺傎偐偵埲壓偺傛偆側墘嶼巕偑偁傝傑偡丅

| 丂墘嶼巕柤徧丂 | 丂墘嶼巕婰崋丂 | 婡擻 | 椺 | 旛峫 |

| 娭學墘嶼巕 | = | 嵍僆儁儔儞僪偲僆儁儔儞僪偑摍偟偄 | if(A = B) | |

| /= | 嵍僆儁儔儞僪偲塃僆儁儔儞僪偼摍偟偔側偄 | if(A /= B) | ||

| < | 嵍僆儁儔儞僪傛傝塃僆儁儔儞僪偑戝偒偄 | if(A < B) | ||

| <= | 嵍僆儁儔儞僪傛傝塃僆儁儔儞僪偑戝偒偄偐摍偟偄 | if( A<= B) | 戙擖偲偟偰傕偙偺婰崋偼巊梡偝傟傞偑僐儞僷僀儔偑暥柆傛傝敾抐偡傞 | |

| > | 嵍僆儁儔儞僪傛傝塃僆儁儔儞僪偑彫偝偄 | if( A > B) | ||

| >= | 嵍僆儁儔儞僪傛傝塃僆儁儔儞僪偑彫偝偄偑摍偟偄 | if( A>= B) | ||

| 壛朄墘嶼巕 | + | 嵍僆儁儔儞僪偵塃僆儁儔儞僪乮掕悢乯傪壛偊傞 | C <= A + B | |

| 尭嶼墘嶼巕 | - | 嵍僆儁儔儞僪偐傜塃僆儁儔儞僪乮掕悢乯傪堷偔 | C <= A - B | |

| 楢寢墘嶼巕 | & | 嵍曈抣乮僆儁儔儞僪乯偲塃曈抣乮僆儁儔儞僪乯傪偮側偖 | signal A: static_logic; signal B: static_logic; signal C: staic_logic_vector(1 downto 0); C <= A & B; |

昗弨偺掕悢傪儀僋僩儖宆偺掕悢偵曄姺偡傞応崌側偳偵梡偄傞 |

| 忔嶼墘嶼巕 | * | 嵍僆儁儔儞僪偲塃僆儁儔儞僪傪偐偗傞 | C <= A * B | |

| 彍嶼墘嶼巕 | / | 嵍僆儁儔儞僪傪塃僆儁儔儞僪偱妱傞 | C <= A / B | |

| 忚梋墘嶼巕 | mod | 嵍僆儁儔儞僪乮旐彍悢丄惍悢乯傪塃僆儁儔儞僪乮彍悢丄惍悢乯偱妱偭偨帪偺梋傝偱丄晞崋偼嵍僆儁儔儞僪乮旐彍悢乯偲 摨晞崋偱偁傞丅傑偨丄偦偺愨懳抣偼彍悢傛傝彫偝偄丅丂C尵岅偺%偲摨偠摦嶌偱偁傞丅 |

C <= A mod B | 11 mode 4 丂 -----亜丂3 -11 mode 4丂 -----亜丂-3 |

| rem | 嵍僆儁儔儞僪乮旐彍悢丄惍悢乯傪塃僆儁儔儞僪乮彍悢丄惍悢乯偱妱偭偨帪偺梋傝偱丄晞崋偼塃僆儁儔儞僪乮彍悢乯偲 摨晞崋偱偁傞丅傑偨丄偦偺愨懳抣偼塃僆儁儔儞僪傛傝彫偝偄丅 |

C <= A rem B | 11 rem 4 丂----亜丂3 -11 rem 4 -----亜丂3 |

|

| 僔僼僩墘嶼巕 | 倱倢倢 | 嵍僆儁儔儞僪偺奺價僢僩傪塃掕悢偩偗嵍僔僼僩偡傞丅嬻偒價僢僩偵偼忢偵0偑擖傞丅 | C <= A sll 2乮2價僢僩嵍傊僔僼僩乯 | 嶼弍嵍僔僼僩 |

| srl | 嵍僆儁儔儞僪偺奺價僢僩傪塃掕悢偩偗塃僔僼僩偡傞丅嬻偒價僢僩偵偼晞崋價僢僩偲摨偠撪梕偑擖傞丅 | C <= A srl 3乮3價僢僩塃傊僔僼僩乯 | 嶼弍塃僔僼僩乮晞崋奼挘偁傝乯 | |

| sla | 嵍僆儁儔儞僪偺奺價僢僩傪塃掕悢偩偗嵍僔僼僩偡傞丅嬻偒價僢僩偵偼忢偵0偑擖傞丅 | C <= A sla 2 | 榑棟嵍僔僼僩 | |

| sra | 嵍僆儁儔儞僪偺奺價僢僩傪塃掕悢偩偗塃僔僼僩偡傞丅嬻偒價僢僩偵偼忢偵0偑擖傞丅 | C <= A sra 3 | 榑棟塃僔僼僩乮晞崋奼挘側偟乯 | |

| rol | 嵍僆儁儔儞僪偺奺價僢僩傪塃掕悢偩偗嵍僔僼僩偡傞丅嬻偒價僢僩偵偼MSB偑擖傞丅 | C <= A rol 2 | 榑棟嵍夞揮 | |

| ror | 塃僆儁儔儞僪偺奺價僢僩傪塃掕悢偩偗塃僔僼僩偡傞丅嬻偒價僢僩偵偼LSB偑擖傞丅 | C <= A ror 3 | 榑棟塃夞揮 | |

| 傋偒忔墘嶼巕 | ** | 嵍僆儁儔儞僪傪塃僆儁儔儞僪乮惍悢乯忔偡傞丅 | C <= A ** 3乮A偺3忔乯 | |

| 愨懳抣墘嶼巕 | abs | 嵍僆儁儔儞僪偺愨懳抣傪庢摼偡傞丅 | C <= abs A |

仭丂奒憌愝寁

丂夞楬傪僐儞億乕僱儞僩壔偟偰丄奒憌愝寁傪偍偙側偆応崌僜乕僗僐乕僪偺婰弎曽幃偲偟偰壓婰偺俁偮偑偁傝傑偡丅

丂丂嘆丂architecture晹偵僐儞億乕僱儞僩柤傪婰嵹偟丄摨堦偺L僜乕僗僼傽僀儖偺拞偵婰嵹偡傞曽幃

丂丂嘇丂architecture晹偵僐儞億乕僱儞僩柤傪婰嵹偟丄忋埵奒憌僜乕僗僼傽僀儖偲偼暿偵僐儞億乕僱儞僩偩偗偺壓埵奒憌僼傽僀儖傪偮偔傝摨堦僨傿儗僋僩儕偵抲偒僐儞僷僀儖偡傞丅

丂丂嘊丂architecture晹偵僐儞億乕僱儞僩柤傪婰嵹偟丄僷僢働乕僕愰尵暥偺拞偱use暥偐傜屇傃弌偡丅